# 500mA Single-Cell Li-Ion Battery Charger with Power Path Management

#### **GENERAL DESCRIPTION**

The SGM41562 is highly integrated, I<sup>2</sup>C programmable, single-cell Li-lon or Li-polymer battery charger with system power path management. It is specifically designed for portable applications requiring minimum board space and small external components. The charging profile includes pre-charge, constant-current and constant-voltage phases. Several safety and protection features are included such as built-in safe charge timer to set maximum duration of charge and pre-charge, input voltage and current monitoring, internal (junction) and external (battery) temperature monitoring, input current limiting and load current limiting. SGM41562 can charge with an input voltage range up to 6V charging range.

The SGM41562 has 3 power ports: input power port (IN), battery port (BAT) and system or load port (SYS). The system is powered from the input whenever it is available. Input is typically a USB power source. If the input source is weak or removed, power source for the system will automatically switch to the battery. The voltage and currents from input and battery as power sources are continuously monitored to prevent battery damage due to excessive currents or over-discharge.

I<sup>2</sup>C serial interface is used to program the device functions and parameters or to read its status. 12 read/write or read only 8-bit registers (REG00 to REG0B) are accessible. A watchdog protection feature is also included. If this feature is enabled and there is no in time read/write activity or signal from the host, the device will reset the charging parameters to their defaults and recycles power to the system (turn off/on) that may reset the host.

The SGM41562 goes into voltage protection state if  $V_{\text{IN}} > 6V$ . The input changes are continuously monitored and a system power recycle (SYS) may occur if the system does not response to the input toggles.

The SGM41562 is available in a Green WLCSP-1.47×1.47-9B package. Device functionality and protection features are assured in the ambient temperature range from -40°C to +125°C. Charging parameters are guaranteed in 0°C to +55°C.

#### **FEATURES**

- Fully Autonomous Charger for Single-Cell Li-lon and Li-Polymer Battery

- 21V Maximum Input Voltage Rating with Over-Voltage Protection

- ±0.6% Charging Voltage Accuracy

- I<sup>2</sup>C Interface for Parameters Setting/Status Reporting

- Fully Integrated Power Switches

- No External Blocking Diode Required

- Built-in Robust Charge Protections Including Battery Temperature Monitor and Programmable Timer

- Battery or PCB Over-Temperature Protection

- System Reset Function

- Built-in Battery Disconnection Function

- Thermal Limit Regulation on Chip

- Available in a Green WLCSP-1.47×1.47-9B Package

#### **APPLICATIONS**

Wearable Devices IoT Gadgets

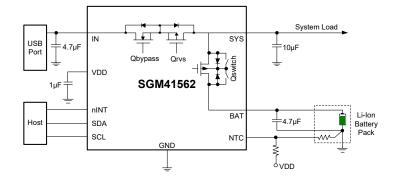

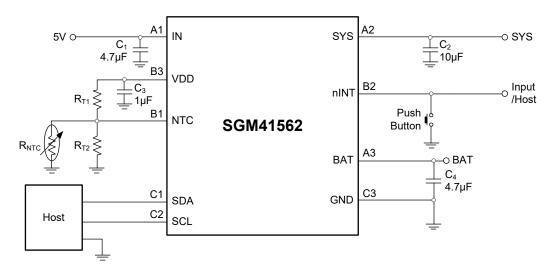

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

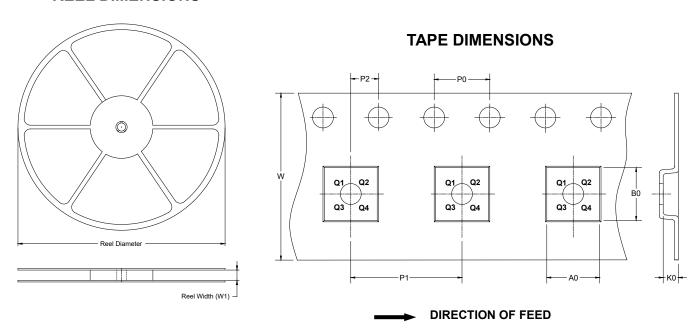

#### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |  |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|--|

| SGM41562 | WLCSP-1.47×1.47-9B     | -40°C to +125°C                   | SGM41562XG/TR      | XXXXX<br>41562     | Tape and Reel, 3000 |  |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN                                  | 0.3V to 21V                   |

|-------------------------------------|-------------------------------|

| SYS                                 | 0.3V to 5.3V (5.5V for 500µs) |

| All Other Pins to GND               | 0.3V to 6V                    |

| I <sub>INCLAMP</sub>                | 5mA                           |

| Package Thermal Resistance          |                               |

| WLCSP-1.47×1.47-9B, θ <sub>JA</sub> | 95°C/W                        |

| Junction Temperature                | +150°C                        |

| Storage Temperature Range.          | 65°C to +150°C                |

| Lead Temperature (Soldering         | , 10s)+260°C                  |

| ESD Susceptibility                  |                               |

| HBM                                 | 3000V                         |

| CDM                                 | 1000V                         |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage, V <sub>IN</sub>       | 4.35V to 5.5V (Charging) |

|---------------------------------------|--------------------------|

| l <sub>IN</sub>                       | Up to 500mA              |

| I <sub>BAT</sub>                      | Up to 3.2A               |

| Існе                                  | Up to 456mA              |

| V <sub>BAT_REG</sub>                  | Up to 4.545V             |

| <b>Operating Junction Temperature</b> |                          |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

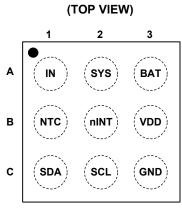

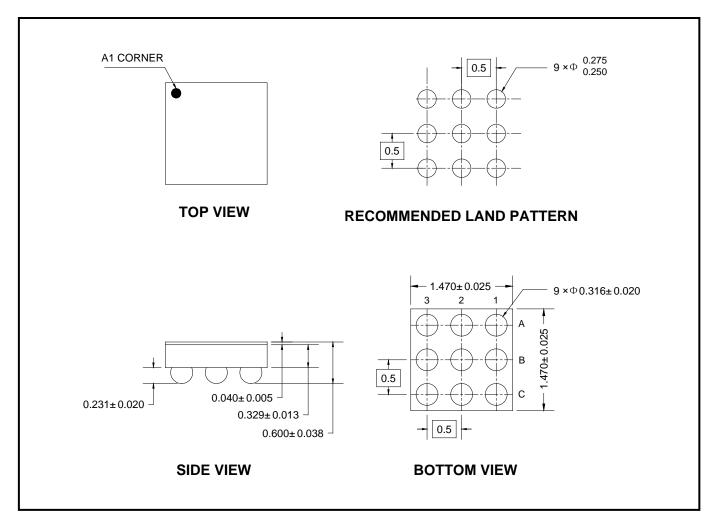

# **PIN CONFIGURATION**

WLCSP-1.47×1.47-9B

# **PIN DESCRIPTION**

| PIN | NAME | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | IN   | Р    | Input Power Pin. Place a minimum 2.2µF ceramic capacitor between IN pin and GND pin as close as possible to these pins.                                                                                                                                                                                                                                                                                                                           |

| A2  | SYS  | Р    | System Power Supply Output. Place a ceramic capacitor between SYS pin and GND pin as close as possible to these pins.                                                                                                                                                                                                                                                                                                                             |

| А3  | BAT  | Р    | Battery Positive Terminal Connection Pin. Place a ceramic capacitor between BAT pin and GND pin as close as possible to the device. Connect the negative battery terminal to power GND.                                                                                                                                                                                                                                                           |

| B1  | NTC  | AIO  | Battery Temperature Sense Input. Connect a negative temperature coefficient thermistor between this pin and GND pin. NTC is usually placed in touch with battery pack. Hot-cold temperature window can be programmed by a resistor divider network placed between VDD to NTC to GND pins. Charging will suspend if NTC function is enabled and NTC pin voltage goes out of the V <sub>HOT</sub> and V <sub>COLD</sub> range.                      |

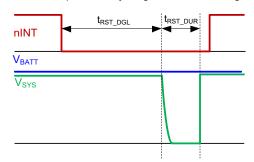

| B2  | nINT | DIO  | Interrupt Output. The nINT pin can send a charging status and fault interrupt signal to the host. nINT is also used to disconnect the system from the battery. Pull nINT pin from high to low for > $t_{RST\_DGL}$ (16s default). The battery FET turns off and turns on again automatically after > $t_{RST\_DUR}$ (4s default) regardless of the nINT state. Both $t_{RST\_DGL}$ and $t_{RST\_DUR}$ can be programmed via the $l^2C$ interface. |

| В3  | VDD  | Р    | Internal Power Supply Pin. Connect a minimum 0.1µF decoupling ceramic capacitor from this pin to GND. External load current on this pin should not exceed 1mA.                                                                                                                                                                                                                                                                                    |

| C1  | SDA  | DIO  | $I^2$ C Bus Data. A 10kΩ pull-up to the logic-high rail should be used on SDA line.                                                                                                                                                                                                                                                                                                                                                               |

| C2  | SCL  | DI   | $I^2$ C Bus Clock. A 10k $\Omega$ pull-up to the logic-high rail should be used on SCL line.                                                                                                                                                                                                                                                                                                                                                      |

| C3  | GND  | _    | Ground Pin of the Device.                                                                                                                                                                                                                                                                                                                                                                                                                         |

NOTE:

AIO = Analog Input and Output; DI = Digital Input; DO = Digital Output; DIO = Digital Input and Output; P = Power.

# **ELECTRICAL CHARACTERISTICS**

$(T_A = +25^{\circ}C, V_{IN} = 5V \text{ and } V_{BAT} = 3.5V, \text{ unless otherwise noted.})$

| PARAMETER                                       | SYMBOL                    | CONDITIONS                                                                                              | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Input Source and Battery Protection             | •                         |                                                                                                         |       |      |       | •     |

| Input Under-Voltage Lockout Threshold           | $V_{IN\_UVLO}$            | Input falling                                                                                           | 3.45  | 3.65 | 3.88  | V     |

| V <sub>IN_UVLO</sub> Threshold Hysteresis       | V <sub>IN_UVLO_HYS</sub>  | Input rising                                                                                            |       | 105  |       | mV    |

| Input Over-Voltage Protection Threshold         | $V_{IN\_OVLO}$            | Input rising threshold                                                                                  | 5.75  | 6    | 6.27  | V     |

| V <sub>IN_OVLO</sub> Threshold Hysteresis       | V <sub>IN_OVLO_HYS</sub>  |                                                                                                         |       | 290  |       | mV    |

| Input Clamp Voltage                             | V <sub>IN_CLAMP</sub>     | Test for having 1mA clamp current                                                                       | 19.5  | 21   |       | V     |

| Input vs. Battery Voltage Headroom<br>Threshold | V <sub>HDRM</sub>         | Input rising vs. battery                                                                                |       | 100  |       | mV    |

| V <sub>HDRM</sub> Threshold Hysteresis          | V <sub>HDRM_HYS</sub>     | Input vs. battery voltage headroom threshold hysteresis                                                 |       | 150  |       | mV    |

| Input Power Detection Time                      | t <sub>PWD</sub>          | Wait time before sending interrupt pulse for reporting input power new status                           | 60    | 70   | 82    | ms    |

| nINT Output Pulse Duration                      | t <sub>INT_PULSE</sub>    |                                                                                                         |       | 250  |       | μs    |

| BAT Pin Input Voltage                           | $V_{BAT}$                 |                                                                                                         |       |      | 4.5   | V     |

|                                                 |                           | V <sub>BAT</sub> falling, VBAT_UVLO[2:0] = 000                                                          | 2.30  | 2.40 | 2.66  | V     |

| Battery Under-Voltage Lockout Threshold         | V <sub>BAT_UVLO</sub>     | V <sub>BAT</sub> falling, VBAT_UVLO[2:0] = 100                                                          | 2.69  | 2.76 | 2.86  |       |

|                                                 |                           | V <sub>BAT</sub> falling, VBAT_UVLO[2:0] = 111                                                          | 2.95  | 3.00 | 3.14  |       |

| Battery Under-Voltage Threshold<br>Hysteresis   | V <sub>BAT_UVLO_HYS</sub> | V <sub>BAT_UVLO</sub> = 2.76V                                                                           |       | 210  |       | mV    |

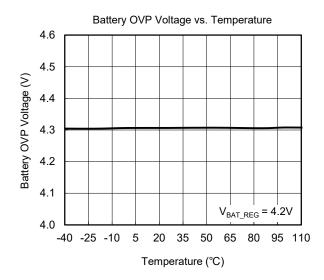

| Battery Over-Voltage Protection Threshold       | $V_{BAT\_OVP}$            | Rising, higher than V <sub>BAT_REG</sub>                                                                |       | 100  |       | mV    |

| Power Path Management                           |                           |                                                                                                         |       |      |       |       |

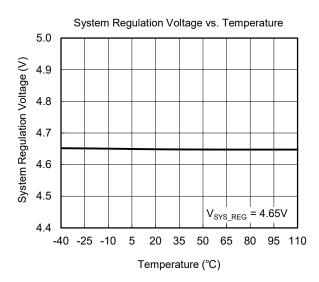

|                                                 |                           | $V_{IN}$ = 5.5V, $R_{SYS}$ = 100 $\Omega$ , $I_{CHG}$ = 0A, VSYS_REG[3:0] = 0000, $V_{SYS}$ REG = 4.2V  | 4.158 | 4.2  | 4.242 |       |

| Regulated System Output<br>Voltage Accuracy     | V <sub>SYS_REG_ACC</sub>  | $V_{IN}$ = 5.5V, $R_{SYS}$ = 100 $\Omega$ , $I_{CHG}$ = 0A, VSYS_REG[3:0] = 1001, $V_{SYS}$ REG = 4.65V | 4.603 | 4.65 | 4.696 | V     |

|                                                 |                           | $V_{IN}$ = 5.5V, $R_{SYS}$ = 100 $\Omega$ , $I_{CHG}$ = 0A, VSYS_REG[3:0] = 1111, $V_{SYS_REG}$ = 4.95V | 4.900 | 4.95 | 4.999 |       |

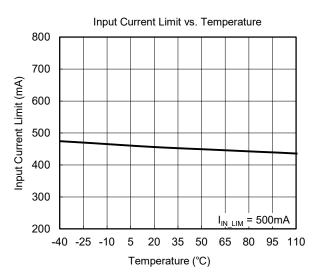

|                                                 |                           | IIN_LIM[3:0] = 0000, I <sub>IN_LIM</sub> = 50mA                                                         |       | 50   |       |       |

| Input Current Limit                             | I <sub>IN LIM</sub>       | IIN_LIM[3:0] = 0011, I <sub>IN_LIM</sub> = 140mA                                                        |       | 140  |       | mA    |

| mpat Ganoni Zimit                               | "IN_LIM                   | IIN_LIM[3:0] = 1001, I <sub>IN_LIM</sub> = 320mA                                                        |       | 320  |       |       |

|                                                 |                           | IIN_LIM[3:0] = 1111, I <sub>IN_LIM</sub> = 500mA                                                        |       | 500  |       |       |

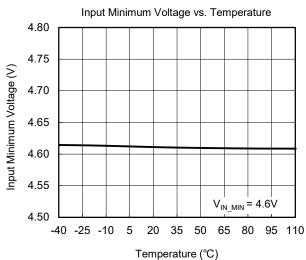

|                                                 |                           | VIN_MIN[3:0] = 0000, V <sub>IN_MIN</sub> = 3.88V                                                        | 3.710 | 3.88 | 4.060 |       |

| Input Minimum Voltage Regulation                | $V_{IN\_MIN}$             | VIN_MIN[3:0] = 1001, V <sub>IN_MIN</sub> = 4.60V                                                        | 4.405 | 4.60 | 4.815 | V     |

|                                                 |                           | VIN_MIN[3:0] = 1111, V <sub>IN_MIN</sub> = 5.08V                                                        | 4.870 | 5.10 | 5.320 |       |

| IN to SYS Switch On-Resistance                  | R <sub>ON_Q1</sub>        | V <sub>IN</sub> = 4.5V, I <sub>SYS</sub> = 100mA                                                        |       | 235  |       | mΩ    |

| Input Quiescent Current                         | I <sub>IN Q</sub>         | $V_{IN}$ = 5.5V, EN_HIZ = 0, CEB = 0,<br>charge enable, $I_{CHG}$ = 0A, $I_{SYS}$ = 0A                  |       | 220  | 265   | μΑ    |

|                                                 | ·114_Q                    | V <sub>IN</sub> = 5.5V, EN_HIZ = 0, CEB = 1, charge disabled                                            |       | 180  | 220   | F", ' |

| Input Suspend Current                           | I <sub>IN_SUSP</sub>      | $V_{IN}$ = 5.5V, EN_HIZ = 1, CEB = 0, charge enable                                                     |       | 50   | 75    | μA    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = +25^{\circ}C, V_{IN} = 5V \text{ and } V_{BAT} = 3.5V, \text{ unless otherwise noted.})$

| PARAMETER                                                                         | SYMBOL                 | CONDITIONS                                                                                                                                                                                                                                                                              | MIN   | TYP   | MAX   | UNITS |  |

|-----------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

|                                                                                   |                        | $V_{IN} = 5V$ , CEB = 0, $I_{SYS} = 0A$ , $V_{BAT} = 4.3V$ ,                                                                                                                                                                                                                            |       | 15    |       |       |  |

|                                                                                   |                        | charge complete $\begin{aligned} &V_{\text{IN}} = \text{GND, CEB} = 1, \text{VDD\_GATE} = 1, \\ &\text{FET\_DIS} = 0, \text{EN\_SHIP\_DGL}[1:0] \neq 11, \\ &I_{\text{SYS}} = 0\text{A, } V_{\text{BAT}} = 4.35\text{V, disable external NTC} \\ &\text{circuit driving} \end{aligned}$ |       | 10    | 40    |       |  |

| Battery Quiescent Current                                                         | I <sub>BAT_Q</sub>     | $V_{\text{IN}}$ = GND, CEB = 1, $I_{\text{SYS}}$ = 0A, $V_{\text{BAT}}$ = 4.35V, enable PCB OTP function, excluding the external NTC bias.                                                                                                                                              |       | 11    |       | μΑ    |  |

|                                                                                   |                        | $V_{\text{IN}}$ = GND, CEB = 1, $I_{\text{SYS}}$ = 0A, $V_{\text{BAT}}$ = 4.35V, enable PCB OTP function and watchdog, excluding the NTC bias.                                                                                                                                          |       | 27    |       | 1     |  |

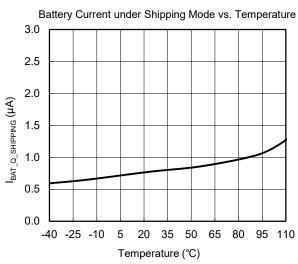

|                                                                                   |                        | V <sub>BAT</sub> = 4.5V, IN is open or grounded, shipping mode                                                                                                                                                                                                                          |       | 0.7   | 1.2   |       |  |

| Battery FET On-Resistance                                                         | R <sub>ON_Q2</sub>     | V <sub>IN</sub> < 2V, V <sub>BAT</sub> = 3.5V, I <sub>SYS</sub> = 100mA                                                                                                                                                                                                                 |       | 100   |       | mΩ    |  |

| Datter FFT Dischause Comment Limit                                                |                        | IDSCHG[3:0] = 0001, I <sub>DSCHG</sub> = 400mA                                                                                                                                                                                                                                          | 295   | 400   | 545   | Л     |  |

| Battery FET Discharge Current Limit                                               | I <sub>DSCHG</sub>     | IDSCHG[3:0] = 1001, I <sub>DSCHG</sub> = 2000mA                                                                                                                                                                                                                                         |       | 2000  |       | mA    |  |

| Delay before Discharge Over Current Cut                                           | t <sub>DSCHG_CUT</sub> | Delay after discharge OC detection and before turning switch off                                                                                                                                                                                                                        |       | 64    |       | μs    |  |

| Delay before Retry after Cut                                                      | t <sub>RETRY</sub>     | Turn on retry delay after OC turn off                                                                                                                                                                                                                                                   |       | 800   |       | μs    |  |

| Ideal Diode Forward Voltage in Supplement<br>Mode (BAT to SYS)                    | $V_{\text{FWD}}$       | 10mA discharge current                                                                                                                                                                                                                                                                  |       | 10    |       | mV    |  |

| Shipping Mode                                                                     |                        |                                                                                                                                                                                                                                                                                         |       |       |       |       |  |

| Enter to Shipping Mode Deglitch Delay<br>Time after Programming the Shipping Mode | t <sub>SMEN_DGL</sub>  | FET_DIS is set from 0 to 1,<br>EN_SHIP_DGL[1:0] = 00                                                                                                                                                                                                                                    |       | 1     |       | s     |  |

| Exit Shipping Mode Delay<br>(Initiated by nINT pin or V <sub>IN</sub> Plug-in)    | t <sub>SMEX_DGL</sub>  | nINT pin is pulled low                                                                                                                                                                                                                                                                  |       | 2     |       | s     |  |

| Auto-Reset Mode                                                                   |                        |                                                                                                                                                                                                                                                                                         |       |       |       |       |  |

| Reset and Power Recycle                                                           | t <sub>RST DGI</sub>   | tRST_DGL[1:0] = 00                                                                                                                                                                                                                                                                      |       | 8     |       | s     |  |

| by nINT Pin is Pull Down                                                          |                        | tRST_DGL[1:0] = 10                                                                                                                                                                                                                                                                      |       | 16    |       |       |  |

| Battery FET Off-Time Duration after Reset                                         | t <sub>RST_DUR</sub>   | tRST_DUR = 0                                                                                                                                                                                                                                                                            |       | 2     |       | e     |  |

| Battery F E F On-Time Buration after Neset                                        | 4RSI_DUR               | tRST_DUR = 1                                                                                                                                                                                                                                                                            |       | 4     |       | s     |  |

| Battery Charger                                                                   |                        |                                                                                                                                                                                                                                                                                         |       |       |       |       |  |

|                                                                                   |                        | VBAT_REG[5:0] = 000000, V <sub>BAT_REG</sub> = 3.6V                                                                                                                                                                                                                                     | 3.564 | 3.600 | 3.636 |       |  |

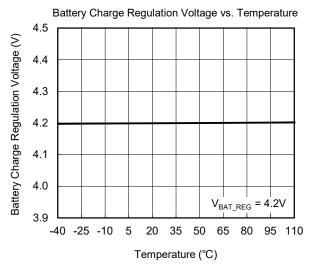

| Battery Charge Regulation Voltage                                                 | $V_{BAT\_REG}$         | VBAT_REG[5:0] = 101000, V <sub>BAT_REG</sub> = 4.2V                                                                                                                                                                                                                                     | 4.175 | 4.200 | 4.225 | V     |  |

| Dattery Charge Regulation Voltage                                                 | ▼ BAT_REG              | VBAT_REG[5:0] = 110100, V <sub>BAT_REG</sub> = 4.38V                                                                                                                                                                                                                                    | 4.354 | 4.380 | 4.406 | V     |  |

|                                                                                   |                        | VBAT_REG[5:0] = 1111111, V <sub>BAT_REG</sub> = 4.545V                                                                                                                                                                                                                                  | 4.518 | 4.545 | 4.572 |       |  |

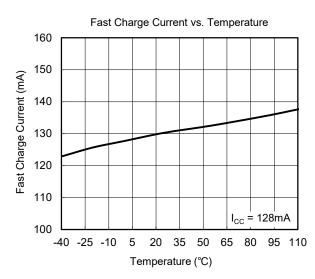

|                                                                                   |                        | ICC[5:0] = 000000, I <sub>CC</sub> = 8mA                                                                                                                                                                                                                                                | 4     | 8     | 10    |       |  |

| Charge Current                                                                    |                        | ICC[5:0] = 001100, I <sub>CC</sub> = 96mA                                                                                                                                                                                                                                               | 84    | 96    | 106   | m A   |  |

| Charge Current                                                                    | Icc                    | ICC[5:0] = 100000, I <sub>CC</sub> = 264mA                                                                                                                                                                                                                                              | 242   | 264   | 300   | mA    |  |

|                                                                                   |                        | ICC[5:0] = 111000, I <sub>CC</sub> = 456mA                                                                                                                                                                                                                                              | 390   | 456   | 520   |       |  |

| Junction Tomporature Population                                                   | т                      | I <sup>2</sup> C programmable range                                                                                                                                                                                                                                                     | 60    |       | 120   | °C    |  |

| Junction Temperature Regulation                                                   | $T_{J_REG}$            | TJ_REG[1:0] = 11, T <sub>J_REG</sub> = 120°C                                                                                                                                                                                                                                            |       | 120   |       |       |  |

|                                                                                   |                        | ITERM[3:0] = 0000, I <sub>TERM</sub> = I <sub>PRE</sub> = 1mA                                                                                                                                                                                                                           | 0.35  | 1     | 1.45  |       |  |

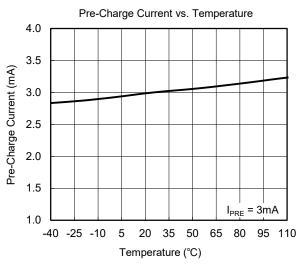

| Pre-Charge Current                                                                |                        | ITERM[3:0] = 0001, I <sub>TERM</sub> = I <sub>PRE</sub> = 3mA                                                                                                                                                                                                                           | 1.25  | 3     | 3.9   | m^    |  |

| r re-onarge ourrent                                                               | I <sub>PRE</sub>       | ITERM[3:0] = 0101, I <sub>TERM</sub> = I <sub>PRE</sub> = 11mA                                                                                                                                                                                                                          | 5.5   | 11    | 14.5  | mA    |  |

|                                                                                   |                        | ITERM[3:0] = 1111, I <sub>TERM</sub> = I <sub>PRE</sub> = 31mA                                                                                                                                                                                                                          | 17    | 31    | 42    |       |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = +25^{\circ}C, V_{IN} = 5V \text{ and } V_{BAT} = 3.5V, \text{ unless otherwise noted.})$

| PARAMETER                                                | SYMBOL                   | CONDITIONS                                                          | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------------|--------------------------|---------------------------------------------------------------------|------|-----|------|-------|

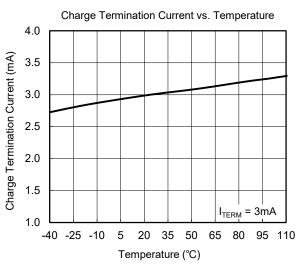

|                                                          |                          | ITERM[3:0] = 0000, I <sub>TERM</sub> = 1mA                          | 0.75 | 1   | 1.15 |       |

| Channa Tamain ation Commant Thursday                     | ,                        | ITERM[3:0] = 0001, I <sub>TERM</sub> = 3mA                          | 2    | 3   | 4    | A     |

| Charge Termination Current Threshold                     | I <sub>TERM</sub>        | ITERM[3:0] = 0101, I <sub>TERM</sub> = 11mA                         | 7    | 11  | 15   | mA    |

|                                                          |                          | ITERM[3:0] = 1111, I <sub>TERM</sub> = 31mA                         | 22   | 31  | 42   |       |

| Termination Deglitch Time                                | t <sub>TERM_DGL</sub>    |                                                                     |      | 200 |      | ms    |

| Pre-Charge to Fast Charge Threshold                      | V <sub>BAT_PRE</sub>     | V <sub>BAT</sub> Rising, VBAT_PRE = 1,<br>V <sub>BAT PRE</sub> = 3V | 2.9  | 3   | 3.1  | V     |

| Pre-Charge to Fast Charge Threshold<br>Hysteresis        | V <sub>BAT_PRE_HYS</sub> |                                                                     |      | 90  |      | mV    |

| Pottory Auto Bookergo Voltago Drop Throshold             | V                        | Below $V_{BAT\_REG}$ , $VRECH = 0$                                  | 110  | 135 | 155  | mV    |

| Battery Auto-Recharge Voltage Drop Threshold             | $V_{RECH}$               | Below V <sub>BAT_REG</sub> , VRECH = 1                              | 210  | 240 | 275  | IIIV  |

| Battery Auto-Recharge Deglitch Time                      | t <sub>RECH_DGL</sub>    |                                                                     |      | 200 |      | ms    |

| Thermal Protection                                       |                          |                                                                     |      |     |      |       |

| Thermal Shutdown Threshold                               | $T_{J\_SHDN}$            |                                                                     |      | 150 |      | °C    |

| Thermal Shutdown Hysteresis                              |                          |                                                                     |      | 20  |      | °C    |

| NTC Pin Output Current                                   | I <sub>NTC</sub>         | CEB = 0, NTC = 3V                                                   | -150 |     | 150  | nA    |

| NTC Cold Temp Rising Threshold                           | V <sub>COLD</sub>        | As percentage of V <sub>DD</sub>                                    | 63   | 65  | 67   | %     |

| NTC Cold Temp Rising Threshold Hysteresis                |                          |                                                                     |      | 30  |      | mV    |

| NTC Hot Temp Falling Threshold                           | V <sub>HOT</sub>         | As percentage of V <sub>DD</sub>                                    | 30   | 33  | 35   | %     |

| NTC Hot Temp Falling Threshold Hysteresis                |                          |                                                                     |      | 70  |      | mV    |

| NTC Hot Temp Falling Threshold for PCB OTP               | V <sub>HOT_PCB</sub>     | As percentage of V <sub>DD</sub>                                    | 30   | 32  | 34   | %     |

| NTC Hot Temp Falling Threshold<br>Hysteresis for PCB OTP |                          |                                                                     |      | 90  |      | mV    |

| Logic IO Pin Characteristics                             |                          |                                                                     |      |     |      |       |

| Low Logic Voltage Threshold                              | $V_L$                    |                                                                     |      |     | 0.4  | V     |

| High Logic Voltage Threshold                             | $V_{H}$                  |                                                                     | 1.4  |     |      | V     |

| I <sup>2</sup> C Interface (SDA, SCL)                    |                          |                                                                     |      |     |      |       |

| Input Low Logic Voltage Threshold                        | V <sub>IL</sub>          |                                                                     |      |     | 0.4  | V     |

| Input High Logic Voltage Threshold                       | V <sub>IH</sub>          |                                                                     | 1.4  |     |      | V     |

| Output Low Threshold Level                               | V <sub>OL</sub>          | I <sub>SINK</sub> = 5mA                                             |      |     | 0.2  | V     |

| I <sup>2</sup> C Clock Frequency                         | f <sub>SCL</sub>         |                                                                     |      |     | 400  | kHz   |

| Clock Frequency and Watchdog Timer                       |                          |                                                                     |      |     |      |       |

| Watchdog Timer                                           | $t_{WDT}$                | WATCHDOG[1:0] = 11                                                  |      | 160 |      | s     |

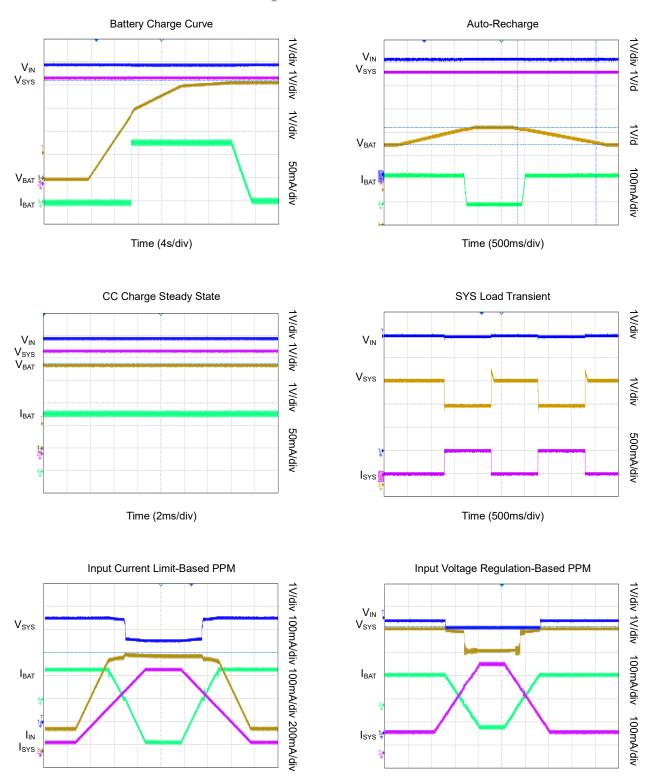

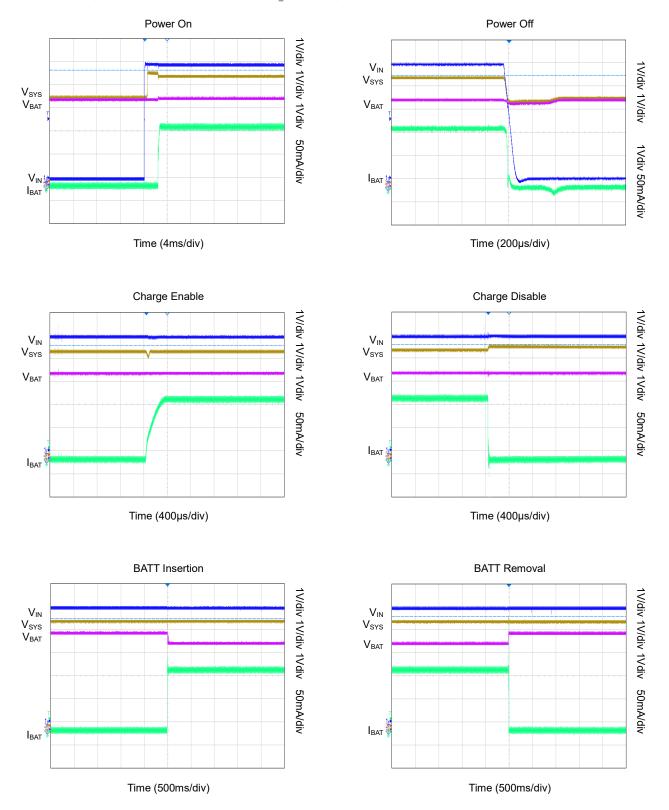

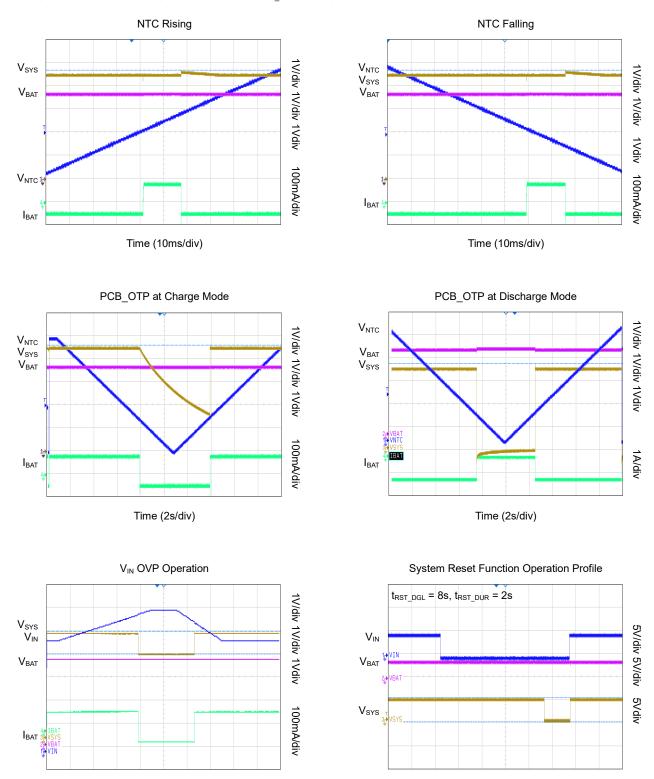

## TYPICAL PERFORMANCE CHARACTERISTICS

Time (4s/div)

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $I_{IN}$  = 500mA,  $I_{CC}$  = 128mA and  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

Time (2s/div)

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $I_{IN}$  = 500mA,  $I_{CC}$  = 128mA and  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $I_{IN}$  = 500mA,  $I_{CC}$  = 128mA and  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

Time (2s/div)

Time (2s/div)

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $I_{IN}$  = 500mA,  $I_{CC}$  = 128mA and  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $I_{IN}$  = 500mA,  $I_{CC}$  = 128mA and  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

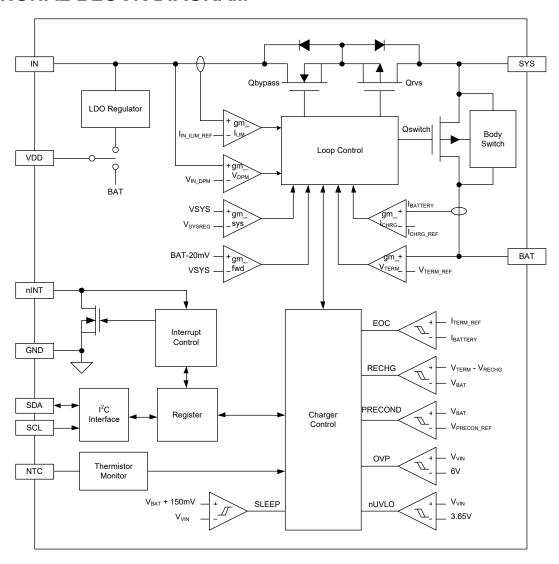

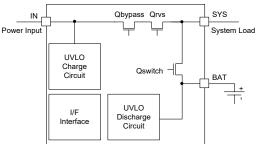

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

## **DETAILED DESCRIPTION**

#### Introduction

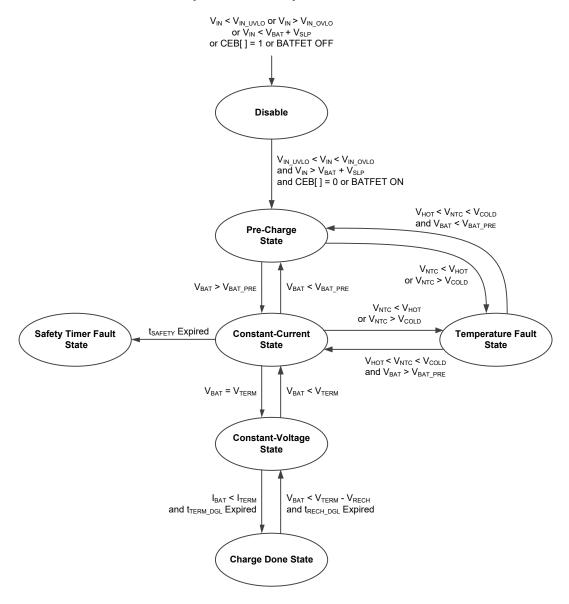

The SGM41562 is a single-cell battery charger with power path management function for Li-lon and Li-polymer batteries. The charge features include pre-charge, fast charge including constant-current mode (CCM) and constant-voltage mode (CVM), end-of-charge termination, auto-recharge, and a built-in safe charge timer. The safe charge timer is used to prevent over-charging or other issues if the host runs out of control.

A bypass switch between IN and SYS pins, and a battery switch between SYS and BAT pins are integrated to provide complete power path management (PPM). The switches have low on-resistances to minimize loss and heat. System load is primarily powered from the input when it is available, and the remaining input power is used to charge the battery if needed. When the input source is weak, the load is powered partially from the battery. This mode in which the battery provides the power deficit, is called supplement mode. Battery will provide the full load power if input is removed or if V<sub>IN</sub> is out of range. For battery charging, the power to the battery is regulated by the battery switch. To prevent faulty charge conditions, input voltage, input current, system voltage, chip temperature and external temperature (sensed by NTC) are continuously monitored during charge.

Figure 3 shows the power paths and key internal blocks of the device. The Qbypass switch regulates the voltage of the system and the internal charge circuit. The Qrvs switch acts as a near ideal blocking diode to prevent reverse power (or leakage) from the load (SYS pin) back to the input (IN pin). The Qswitch switch is responsible for battery charging regulation and connecting or disconnecting of the battery (BAT pin) to the system (SYS pin). The charge and discharge circuits in the Figure 3 that are connected to the IN and BAT pins have their own independent UVLO and power supply. The rest of the chip is powered by either IN or SYS pin, whichever has the higher voltage. The I/F interface (I<sup>2</sup>C communication and nINT) block is active whenever any of the power sources (IN or BAT pin) are available.

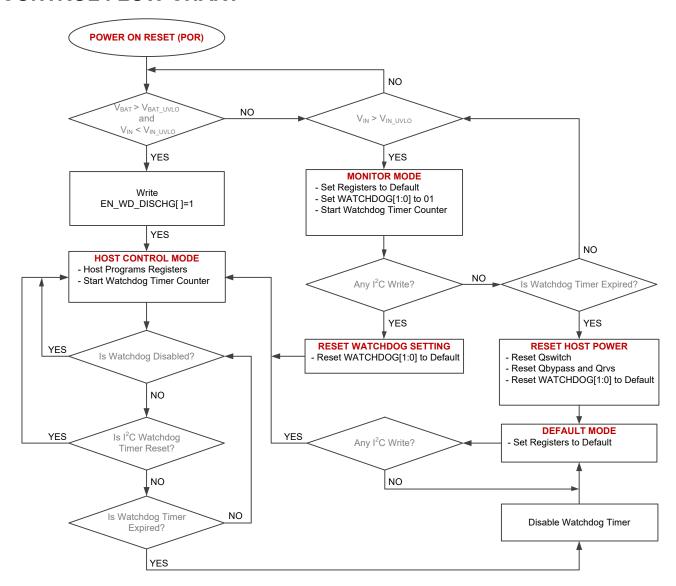

Figure 3. Power Path Management Structure

The chip has a watchdog timer as a protective feature against unexpected host malfunctions. When watchdog timer is enabled, it must be reset by host regularly to prevent watchdog timer overflow that results in a chip reset and power recycle. Watchdog reset is by writing into the watchdog register through I<sup>2</sup>C interface (I/F). If the watchdog is not reset on time, the power to the host will recycle.

The power fed to the SYS pin is recycled when watchdog times out, the host does not response to IN power input (when watchdog is forced on) or COLD\_RESET bit is set to 1, to clear the running environment before system program upgrade or release from locked situations.

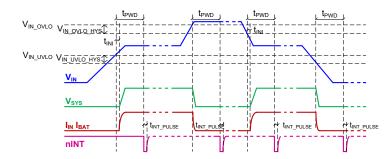

#### **Input Detection**

Figure 4 shows how the input voltage status is detected and affects the device function along with the relevant timings and nINT output signal updates. The device continuously monitors the input voltage at the IN node. The SYS node and charge circuit is only started and connected to the input when for a duration of  $t_{\rm INI}$ ,  $V_{\rm IN}$  is within its normal range (above  $V_{\rm IN\_UVLO}$  and below  $V_{\rm IN\_OVLO}$ ). Qbypass and Qrvs switches will turn off as soon as an input UVLO or OVLO is detected.

As shown in Figure 4 any input state is considered stable if it continuously stays in the same condition for a duration of  $t_{PWD}$  after which the device sends out a negative pulse to the nINT pin with a pulse width of  $t_{INT\_PULSE}$  to inform the host about the input state change.

The watchdog timer WATCHDOG[1:0] register is set to 01 once the valid input is detected and when an INT pulse is asserted, which resumes its original setting when any writing to this device occurs. If the host does not clear the watchdog, power to the host is recycled for reset when watchdog runs time out.

Figure 4. Input Power Detection and nINT Signaling Timings

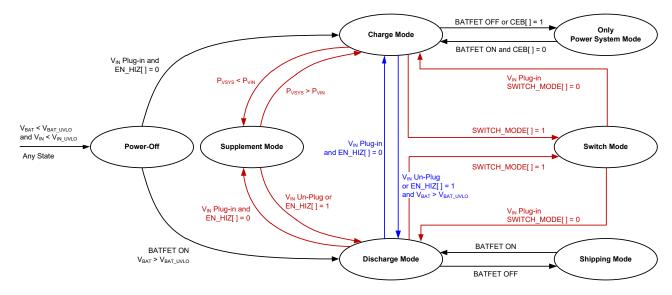

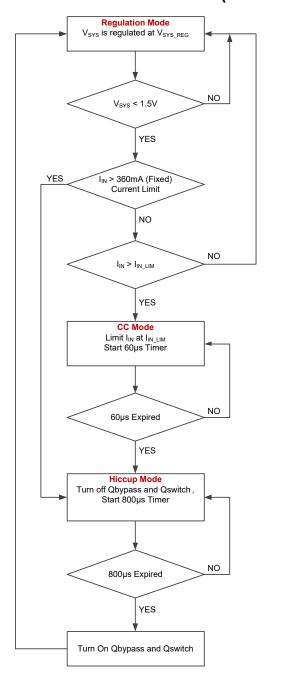

#### **Power Path Management**

When the input voltage is normal and have enough headroom for powering the system ( $V_{IN} > V_{IN\_UVLO}$  and  $V_{IN} - V_{SYS} > V_{HDRM}$ ), the input power path will conduct and the device starts to power the system from input by setting the system voltage to  $V_{SYS\_REG}$ .  $V_{SYS\_REG}$  is selected by programming VSYS\_REG[3:0] register, the lower 4 bits of REG07 (also called system voltage register or VSYS\_REG[3:0] register). However, the actual system voltage ( $V_{SYS}$ ) can be affected by the input voltage level, input current limit and battery voltage.

I<sup>2</sup>C commands can directly control the power paths. Input path will be disconnected (high-impedance) by turning off Qbypass switch if the EN\_HIZ bit is set to 1. If the battery is getting charge and Qswitch switch is on, it can also be disconnected by setting charge enable bit, set the CEB bit to 1 (turn off Qswitch switch in charge direction). The power path control bits are explained in Table 1. When these bits are clear, they have no effect.

Table 1. Switch Control by I<sup>2</sup>C Interface

| FETs                  | EN_HIZ = 1 | CEB = 1 |

|-----------------------|------------|---------|

| Qbypass               | Off        | X       |

| Qswitch (Charging)    | Х          | Off     |

| Qswitch (Discharging) | X          | Х       |

NOTE: X = Don't Care.

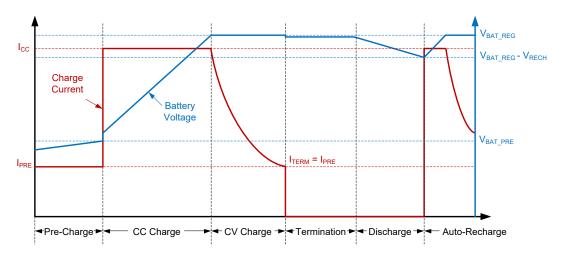

#### **Battery Charge Profile**

Figure 5 shows the battery charge profile used in this device. The charge phases are explained below. Depending on the I<sup>2</sup>C settings and the battery state of charge (SOC), some or all of the phases may be skipped or used to finish a complete charge cycle as explained below:

**Pre-Charge**: If the battery voltage is less than the pre-charge threshold ( $V_{BAT\_PRE}$ ), the battery is charged with the small pre-charge current ( $I_{PRE}$ ). The pre-charge current value is the same as the termination current ( $I_{TERM}$ ) that is programmed via bit D[3:0] of the REG03, also called ITERM[3:0].

**Constant-Current Charge**: When battery voltage is higher than  $V_{BAT\_PRE}$ , and less than  $V_{BAT\_REG}$ , it will be charged with a constant current. The constant-current value is determined by bit D[5:0] of the REG02 that is called ICC[5:0] and a single scaling bit that if set, multiplies it by 1⁄4. This bit is used for finer CC adjustment (CC FINE bit in REG0A).

**Constant-Voltage Charge**: When the battery voltage reaches to the  $V_{BAT\_REG}$ , the voltage is kept constant and the charge current drown by battery will start to fall. The  $V_{BAT\_REG}$  value is determined by bit D[7:2] of the REG04 that is also called VBAT\_REG[5:0].

**Charge Termination**: A charge termination is recognized when the charge current drops to a small value represented by  $I_{TERM}$ . If the termination detection is enabled by setting the EN\_TERM bit in REG05 D[4] to 1, then if the charge current ( $I_{CHG}$ ) stays equal or lower than  $I_{TERM}$  for a period of  $t_{TERM\_DGL}$  (termination deglitching time) the charge cycle is considered complete and charging current will be turned off and drop to zero. With no termination, the charge current will continue to drop. Note that a charge cycle is also considered complete and charging will be turned off, if the safe timer function runs out of time provided that the safe timer function is already enabled by setting EN\_TIMER bit in REG05 D[3] to 1.

Figure 5. Battery Charge Profile

The charge status is updated to "charge complete" once the termination condition is detected. The charge current will be terminated when termination conditions are met and if the TERM\_TMR bit is set to 0 (REG05 D[0] = 0); The charge will not terminate and current keeps decreasing if TERM\_TMR bit is 1.

During the whole charging process, the actual charge current may fall below the set values due to the other regulations or controls such as dynamic power management (DPM) regulation caused by insufficient input voltage or current or due to thermal regulation. In thermal regulation the device reduces the power path currents to keep junction temperature below the programmed limit.

A new charge cycle starts when one of the following conditions occurs:

- The input power recycles (input on/off).

- Battery charging is enabled by I<sup>2</sup>C command.

- Auto-recharge kicks in due to battery charge state.

If all the following conditions are satisfied:

- · No NTC thermistor temperature fault.

- No safety (charge) timer fault.

- No battery over voltage event.

- The Qswitch switch is not forced to turn off (e.g. CEB = 1).

#### **Battery Over-Voltage Protection**

SGM41562 has a built-in battery over-voltage protection limit. A battery over-voltage event is detected when battery voltage is higher than  $V_{\text{BAT\_OVP}} + V_{\text{BAT\_REG}}$ . When this event occurs, the charging is immediately suspended and a fault is asserted. The discharging path will be turned on if battery over-voltage condition does not clear and continues.

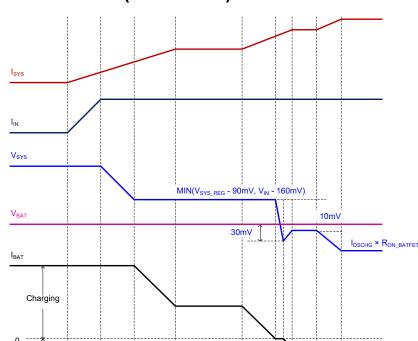

# Input Current and Input Voltage Based Power Management

Usually the input source (typically USB) is not strong enough for all system power demands and a power management scheme is needed to keep the system voltage in desired level without over loading the source. Figure 6 shows the power management profile and explains how it is implemented in SGM41562 including the battery assist operation (supplement) when input source is not able to provide required power.

The input current is continuously monitored to make sure the input source maximum current limit specification is met. The total input current limit is programmable by I<sup>2</sup>C and is used to prevent over loading of the input source.

If the input source is weak and the programmed input current limit is higher than the effective capability of the source (like in a dynamic loading condition) the back-up power management will come in effect to prevent over loading of the input source. The back-up power management is based on limiting the input voltage drop to  $V_{\mathsf{IN\_MIN}}$  value (programmable). The voltage based dynamic power management (DPM) will regulate the input voltage to  $V_{\mathsf{IN\_MIN}}$  when the load is higher than the input current capacity. If input current and voltage limit are both reached, then the Qbypass switch (between IN and SYS pins) will regulate and limit the total power taken from the input. With the power limiting, if the system voltage drops to the minimum value of ( $V_{\mathsf{SYS\_REG}}$  - 90mV) or the input voltage falls below ( $V_{\mathsf{IN}}$  - 160mV), the device will finally reduce the charge current to prevent further voltage drops.

The programmed  $V_{\text{IN\_MIN}}$  must be at least 250mV higher than  $V_{\text{BAT\_REG}}$  to assure stable operation of the regulator.

Figure 6. Dynamic Power Management and Battery Supplement Operation Profile

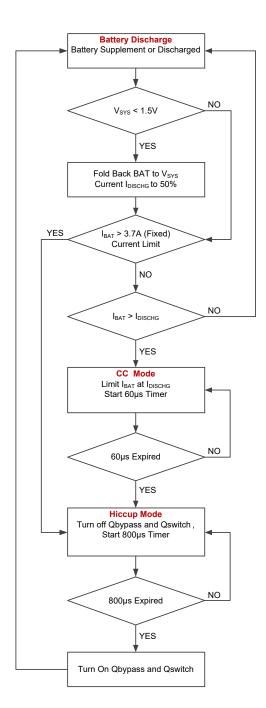

#### **Battery Supplement Mode**

As mentioned above, the DPM will reduce the charge current to keep the input current or voltage in regulation when source power is not sufficient for system demand. If the charge current is reduced to zero but still due to heavy system load the input source is overloaded and  $V_{SYS}$  continues to drop, then the battery will supply the deficit to assist the input source. This mode is called battery supplement mode in which the battery provides I<sub>DSCHG</sub> as supplement current to the load. This mode starts when the system drop reaches to 30mV below the battery voltage. In this mode the Qswitch switch acts as a near ideal diode from battery to the system. The Qswitch switch is controlled to regulate and maintain the  $V_{BAT}$  -  $V_{SYS}$  drop to a fixed 10mV value when  $I_{DSCHG}$  × Ron BATFET is less than 10mV. If IDSCHG × RON BATFET is larger than 10mV, the Qswitch switch is fully turned on to pass battery voltage to the system with minimum drop.

Discharging

In the battery supplement mode the ideal diode mode will be disabled as soon as the system load decreases and  $V_{\text{SYS}}$  exceeds the  $V_{\text{BAT}}$  + 20mV value.

When  $V_{\text{IN}}$  source is not available, the device operates in discharge mode (battery power) in which the Qswitch switch is always fully on to reduce the losses.

#### **Battery Regulation Voltage**

The battery voltage for the constant-voltage regulation phase (CV) is represented by  $V_{\text{BAT}}$  REG.

#### Thermal Regulation and Shutdown

SGM41562 continuously monitors its internal junction temperature to avoid junction overheating while keeping the power delivery at its maximum. When the internal junction temperature reaches its programmable limit (T<sub>J\_REG</sub>), the device starts to reduce the charge current to prevent higher power dissipation. The thermal regulation limit is programmable to help adjusting the design for the thermal requirements in different applications. 4 different junction temperature regulation thresholds can be chosen by programming the TJ\_REG[1:0] register.

The device fixed thermal shutdown limit ( $T_{J\_SHDN}$ ) is slightly higher than the highest programmable  $T_{J\_REG}$ . If  $T_{J}$  rises above this limit, both Qbypass and Qswitch switches will turn off.

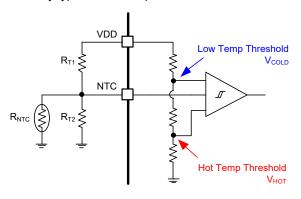

#### **NTC Function and VDD Gating**

The NTC pin is provided to sense the battery temperature using an NTC thermistor. Thermistors are usually included in the rechargeable battery packs to ensure safe operation by monitoring the battery temperature and making sure it is between hot and cold limits. To adjust the temperature limits for the device, two resistors (R<sub>T1</sub> and R<sub>T2</sub> in Figure 13) should be connected to NTC pin as a divider between VDD and GND pins. The thermistor itself is connected between NTC pin and GND. The voltage on the NTC pin is determined by all three resistors. This resistor divider along with the hot and cold limit voltages defined in the EC table determines the hot-cold operating window. Note that due to the negative temperature coefficient of NTC, when its voltage drops below V<sub>HOT</sub>, it means the battery temperature is exceeding the hot limit. The NTC protection function can be disabled by clearing the EN\_NTC bit to 0. The default settings for NTC function are the PCB OTP levels specified in EC table that can be change by I<sup>2</sup>C as explained in Table 2.

**Table 2. NTC Function Selection**

| I <sup>2</sup> C Ce | I <sup>2</sup> C Control |          |  |  |  |

|---------------------|--------------------------|----------|--|--|--|

| EN_NTC              | EN_PCB OTP               | Function |  |  |  |

| 0                   | don't care               | Disable  |  |  |  |

| 1                   | 1                        | NTC      |  |  |  |

| 1                   | 0                        | PCB OTP  |  |  |  |

NTC function only works in charge mode. When NTC pin voltage falls out of the hot-cold window it means that the temperature is outside the safe operating range and results in a pause in charging and sets the fault bits. Charging will resume when the temperature falls back into the safe range.

If DIS\_VDD bit is disabled and  $V_{IN}$  is removed,  $V_{DD}$  power turns off and becomes high-impedance leaving only  $R_{T2}$  in parallel with the NTC thermistor. If DIS\_VDD bit is enabled,  $V_{DD}$  remains active.  $V_{DD}$  uses battery power if  $V_{IN}$  is removed.

With PCB OTP selected, if the NTC pin voltage is lower than the NTC hot threshold, Qbypass and Qswitch switches will turn off. The PCB OTP fault also will set the NTC\_FAULT status bit to 1. The operation will resume when the NTC pin voltage goes back above the NTC hot threshold.

#### Safety Timer

Using an internal safety timer, SGM41562 is capable to limit the maximum duration of the pre-charge and charge periods to avoid extended charging cycles that may happen due to abnormal battery conditions. This protection can be disabled by I<sup>2</sup>C. The safety timer starts counting if one of the following occurs:

- A new charge cycle is started.

- Write in REG01 D[3] bit: from 1 to 0 (charge enable)

- Write in REG05 D[3] bit: from 0 to 1 (safety timer enable)

- Write in REG02 D[7] bit: from 0 to 1 (software reset)

- Write in REG0A D[4] bit: from 0 to 1 (software power recycle) The safety time limit is 1 hour for pre-charge condition in which the battery voltage stays lower than V<sub>BAT\_PRE</sub> and cannot go higher. For the charge phase the time limit is programmable through I<sup>2</sup>C and the safety timer starts counting when the battery enters in constant-current charge mode or constant-voltage charge mode.

#### **Host Mode and Default Mode**

SGM41562 can operate in either default mode (with default parameters) or host mode (parameters programmed by host). It will go to the default mode if one of the following occurs:

- · Input refresh with no battery connected.

- Re-insert battery with no input source connected.

- Device registers reset by writing 1 to REG RST bit.

- Watchdog timer expiry.

Upon a power on reset, the device starts in default mode and in the same state as if watchdog timer expiration has occurred. In this mode all registers take their default values, including EN\_HIZ = 0 and CEB = 1, that means the input power path is enabled and device is set to battery discharge mode. Note that by default the battery will not be charged after a reset.

When the device is in the host mode, watchdog function can be activated and works in both charge and discharge modes (Watchdog timer is independent of the charge safety timer). Watchdog timer can be enabled by programming a non-zero expiry time in its register, that is WATCHDOG[1:0]  $\neq$  00. If watchdog timer is enabled, it must be reset regularly before it runs out of time by writing 1 to WD\_RST bit in REG02. Otherwise the watchdog timer will expire and results in a power recycle to the system. Therefore, resetting the watchdog timer by host must happen in the intervals shorter than watchdog time limit. The power recycle is performed by turning off Qswitch and Qbypass for a duration of  $t_{RST\_DUR}$  and then turning them on again. After watchdog timer expiration, all registers will reset to their default values and the device goes to the default mode.

To reduce the quiescent current during discharge mode, the watchdog timer can be turned off by setting the EN\_WD\_DISCHG bit to 0. If the WATCHDOG[1:0] is set to 00, the watchdog timer is disabled under charge and discharge modes independent of the EN\_WD\_DISCHG bit value.

#### **Battery Discharge Function**

If the battery is connected ( $V_{BAT}$  is above the  $V_{BAT\_UVLO}$  threshold) and the input source is missing, the Qswitch turns fully on. The low on resistance of the Qswitch minimizes the conduction loss during discharge. The quiescent current of the device is as low as 11µA in this mode. By setting REG0A D[3] bit to 1, the Qswitch will stay on even if the rest of the internal blocks are turned off, to reduce the device quiescent current to less than 1.2µA. The low on-resistance and low quiescent current of the device extend the run time.

#### **Over-Discharge Current Protection**

The over-discharge current protection is effective in discharge mode and supplement mode. If the  $I_{BAT}$  exceeds discharge current limit value programmed in the REG03 D[7:4], the Qswitch turns off after a wait delay ( $t_{DSCHG\_CUT}$ ) and then resumes conducting after a retry delay time ( $t_{RETRY}$ ). Qswitch turns off instantly if the discharge current exceeds 3.7A value.

When the battery voltage falls below the  $V_{BAT\_UVLO}$  limit that is programmed in the REG01 D[2:0], the Qswitch turns off to prevent over discharging the battery.

If SWITCH\_MODE bit (REG0A D[3]) is set to 1, the Qswitch is forced to remain on like a simple switch and the over-discharge is ignored during battery discharge. This bit will reset if power is re-applied to the input. It will also reset if the battery is connected or disconnected while power is applied to the input.

#### **System Short Circuit Protection**

If a short circuit (to GND) occurs on the load connected to SYS pin, the Qswitch disconnects the BAT to SYS path and the Qbypass limits the current flowing in the IN to SYS path. If the short circuit persists, the die temperature goes high and causes a thermal shutdown.

#### Interrupt to Host (nINT Pin)

The nINT output signal is provided to alert the host on power events. SGM41562 sends out a negative pulse (width =  $t_{\text{INT PULSE}}$ ) to nINT if any of the following events occurs:

- A good input source is detected (UVLO < V<sub>IN</sub> < OVLO).</li>

- UVLO or OVLO is detected (input).

- Charge completed.

- A charging status change.

- A fault record in REG09 occurs (input fault, thermal fault, safety timer fault, battery OVP fault or NTC fault).

- Watchdog expiration (WTD\_FAULT in REG08 D[7]).

When one of the mentioned faults occurs, the relevant fault bit will latch in the register except for NTC fault bit that always reports the current status of the thermistor. A fault status bit is unlatched if the device quits that fault state. It will reset to 0 after the host reads the register if the bit is unlatched.

The assertion of nINT signal pulse can be masked for some of the events listed above when the corresponding mask control bits are set in REG06 D[4:0]. If a mask bit is set, and the event occurs, the nINT signals stays high.

The nINT pin is also used as an input to initiate a power recycle on the SYS output for example when a turn off/turn on is needed on the system when battery is not removable. This input is also used to exit the shipping mode that keeps the battery disconnected. The nINT pin is weakly pulled up internally to an unregulated low voltage that is not high enough for most logic devices. The weak and low voltage pull-up is used to avoid unexpected battery drain or leakage when the product is in shipping or is stocked for prolonged times (called shipping mode). The pull-up can be overdriven externally to higher appropriate logic voltages when it is in operation.

#### **Battery Disconnection Function**

When the battery is not removable, it's essential to disconnect the battery from the system to allow system power recycling or to put that in the shipping mode. It is performed by forcing the Qswitch to remain off by setting FET\_DIS bit to 1. Table 3 explains how the SGM41562 can be programmed in shipping mode (or to do a power recycle on SYS) and how to exit the shipping mode. To exit shipping mode either the input power should be applied to IN port, or a low voltage (ground) should be applied to nINT pin for a short time (for example by holding a push bottom).

**Table 3. Shipping Mode Control**

|                       | Enter Shipping Mode | Exit Shipping Mode        |                         |  |  |

|-----------------------|---------------------|---------------------------|-------------------------|--|--|

| Items                 | FET_DIS = 1         | nINT Pin<br>H to L for 2s | V <sub>IN</sub> Plug-in |  |  |

| Qbypass               | don't care          | don't care                | On                      |  |  |

| Qswitch (Charging)    | Off                 | On                        | On (64ms Later)         |  |  |

| Qswitch (Discharging) | Off                 | On                        | On (64ms Later)         |  |  |

The FET\_DIS bit is used for battery disconnection control. If this bit is set to 1, the device enters shipping mode after a delay time, which can be programmed by EN\_SHIP\_DGL[1:0]. After the delay the Qswitch turns off and the FET\_DIS bit resets to 0. The device wakes up from shipping mode by pulling down nINT pin or detecting an acceptable voltage on the IN pin. The device exits from shipping mode 2 seconds after pulling nINT pin down or 64ms after detecting an acceptable  $V_{\text{IN}}.$  For the application of nINT pulled down to a low voltage in the shipping mode, EN\_SHIP\_DGL[1:0] must keep default value.

System power can be recycled by turning off the Qswitch and Qbypass if nINT pin is pulled low for a duration of more than  $t_{RST\_DGL}$ . It is the time delay to avoid noise and glitches or to hold a push bottom. The  $t_{RST\_DGL}$  time is programmed by  $t_{RST\_DGL}$ [1:0] in REG01. The off state lasts for a duration of  $t_{RST\_DUR}$  which can be programmed via  $t_{RST\_DUR}$  in REG01. After this time the Qswitch and/or Qbypass will be automatically turned on and the system is powered again. During the off period, the nINT pin is biased to a lower voltage.

The waveforms of power recycling are shown in Figure 7.

Figure 7. Power Recycling Waveforms

## **REGISTER MAP**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB).

## I<sup>2</sup>C Slave Address is: 03H

R/W: Read/Write bit(s).

R: Read only bit(s).

PORV: Power-On-Reset value.

n: Parameter code formed by the bits as an unsigned binary number.

#### REG00

Register address: 0x00; R/W

PORV = 10011111

#### Table 4. REG00 Register Details

| BITS   | BIT NAME                                               | DESCRIPTION                          | COMMENT                                                        | PORV | TYPE    | RESET BY |

|--------|--------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|------|---------|----------|

|        | 1 = 640mV<br>VIN_MIN[2<br>1 = 320mV                    | VIN_MIN[3]<br>1 = 640mV              | Minimum Input Voltage Limit (n: 4 bits):<br>= 3.88 + 0.08n (V) | 1    | R/W     | REG_RST  |

| D[7:4] |                                                        | VIN_MIN[2]<br>1 = 320mV              | Offset: 3.88V                                                  | 0    | R/W     | REG_RST  |

| D[7.4] | V II V_   W   II V   J   J   J   J   J   J   J   J   J | VIN_MIN[3:0]                         | 0                                                              | R/W  | REG_RST |          |

|        |                                                        | VIN_MIN[0]<br>1= 80mV                |                                                                | 1    | R/W     | REG_RST  |

|        |                                                        | IIN_LIM[3]<br>1 = 240mA              | Input Current Limit (n: 4 bits):<br>= 50 + 30n (mA)            | 1    | R/W     | REG_RST  |

| D[3:0] | IIN LIM[3:0]                                           | IIN_LIM[2]<br>1 = 120mA Offset: 50mA |                                                                | 1    | R/W     | REG_RST  |

| D[0.0] | IIIV_LIM[3.0]                                          | IIN_LIM[1]<br>1= 60mA                | Range: 50mA (0000) - 500mA (1111) Default: 500mA (1111)        | 1    | R/W     | REG_RST  |

|        |                                                        | IIN_LIM[0]<br>1 = 30mA               |                                                                | 1    | R/W     | REG_RST  |

#### REG01

Register address: 0x01; R/W

PORV = 10101100

#### Table 5. REG01 Register Details

| BITS   | BIT NAME       | DESCRIPTION                                                           | COMMENT                                                                                                                     | PORV | TYPE | RESET BY               |

|--------|----------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------------------------|

| D[7:6] | +DCT_DC1[1:0]  | 00 = 8s<br>01 = 12s                                                   | nINT Pull-Down Period to Disconnect the Battery (n: 2 bits):                                                                | 1    | R/W  | REG_RST or Watchdog    |

| D[7:6] | tRST_DGL[1:0]  | 10 = 16s (default)<br>11 = 20s                                        | = 8s + 4n (seconds)                                                                                                         | 0    | R/W  | REG_RST or Watchdog    |

| D[5]   | tRST_DUR       | 0 = 2s<br>1 = 4s (default)                                            | Battery FET off-time duration after reset. The Qbypass and Qswitch off-time before auto turn-on.                            | 1    | R/W  | REG_RST<br>or Watchdog |

| D[4]   | EN_HIZ         | HIZ Mode Enable<br>0 = Disable (default)<br>1 = Enable                | Control Qbypass switch. Default: disable (0) or switch on Note: The EN_HIZ bit only controls the on and off of the Qbypass. | 0    | R/W  | REG_RST<br>or Watchdog |

| D[3]   | CEB            | Setting Charge Enable 0 = Charge Enable 1 = Charge Disabled (default) | Charge enable/disable Qswitch configuration. Default: charge disabled (1) or Qswitch off                                    | 1    | R/W  | REG_RST<br>or Watchdog |

|        |                | VBAT_UVLO[2]<br>1 = 360mV                                             | Battery UVLO Threshold Value (n: 3 bits):<br>= 2.4V + 0.09n (V)                                                             | 1    | R/W  | REG_RST<br>or Watchdog |

| D[2:0] | VBAT_UVLO[2:0] | VBAT_UVLO[1]<br>1 = 180mV                                             | Offset: 2.4V                                                                                                                | 0    | R/W  | REG_RST or Watchdog    |

|        |                | VBAT_UVLO[0]<br>1 = 90mV                                              | Range: 2.4V (000) - 3.03V (111)<br>Default: 2.76V (100)                                                                     | 0    | R/W  | REG_RST or Watchdog    |

## REG02

Register address: 0x02; R/W

PORV = 00001111

#### Table 6. REG02 Register Details

| BITS   | BIT NAME | DESCRIPTION                                                                | COMMENT                                                                                                 | PORV | TYPE | RESET BY               |

|--------|----------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------------------------|

| D[7]   | REG_RST  | Software Reset<br>0 = Keep Current Setting<br>(default)<br>1 = Reset       | If set, will reset most parameters to default. (as explained in the last column of register map tables) | 0    | R/W  | REG_RST                |

| D[6]   | WD_RST   | I <sup>2</sup> C Watchdog Timer Reset<br>0 = Normal (default)<br>1 = Reset | If set, will reset watchdog timer.                                                                      | 0    | R/W  | REG_RST<br>or Watchdog |

|        |          | ICC[5]<br>1= 256mA                                                         | Fast Charge Current Value (CC Mode)<br>(n: 5 bits): = 8mA + 8n (mA) (n ≤ 56)                            | 0    | R/W  | REG_RST<br>or Watchdog |

|        |          | ICC[4]<br>1 = 128mA                                                        | Offset: 8mA                                                                                             | 0    | R/W  | REG_RST<br>or Watchdog |

| D(E:0) | ICCIE:01 | ICC[3]<br>1 = 64mA                                                         | Range: 8mA (000000) - 456mA (111000)<br>Default: 128mA (001111)                                         | 1    | R/W  | REG_RST or Watchdog    |

| D[5:0] | 100[5.0] | ICC[5:0] ICC[2] 1 = 32mA                                                   | Note:<br>Values above 56D = 111000 (456mA) are<br>clamped to 56D = 111000 (456mA).                      | 1    | R/W  | REG_RST<br>or Watchdog |

|        |          | ICC[1]<br>1 = 16mA                                                         |                                                                                                         | 1    | R/W  | REG_RST or Watchdog    |

|        |          | ICC[0]<br>1 = 8mA                                                          |                                                                                                         | 1    | R/W  | REG_RST<br>or Watchdog |

#### REG03

Register address: 0x03; R/W

Table 7. REG03 Register Details

| BITS   | BIT NAME    | DESCRIPTION             | COMMENT                                                                          | PORV | TYPE | RESET BY               |

|--------|-------------|-------------------------|----------------------------------------------------------------------------------|------|------|------------------------|

|        |             | IDSCHG[3]<br>1 = 1600mA | BAT to SYS Discharge Current Limit Value (n: 4 bits): = 200mA + 200n (mA), n ≠ 0 | 1    | R/W  | REG_RST<br>or Watchdog |

|        |             | IDSCHG[2]<br>1 = 800mA  | Offset: 200mA                                                                    | 0    | R/W  | REG_RST<br>or Watchdog |

| D[7:4] | IDSCHG[3:0] | IDSCHG[1]<br>1 = 400mA  | Valid Range: 400mA (0001) - 3.2A (1111)  Default: 2000mA (1001)                  | 0    | R/W  | REG_RST<br>or Watchdog |

|        |             | IDSCHG[0]<br>1 = 200mA  |                                                                                  | 1    | R/W  | REG_RST<br>or Watchdog |

|        |             | ITERM[3]<br>1 = 16mA    | Charge Termination Current Value (n: 4 bits):<br>= 1mA + 2n (mA)                 | 0    | R/W  | REG_RST<br>or Watchdog |

| D[2.0] | ITEDM(0.0)  | ITERM[2]<br>1 = 8mA     | Offset: 1mA Range: 1mA (0000) - 31mA (1111) Default: 3mA (0001)                  | 0    | R/W  | REG_RST<br>or Watchdog |

| D[3:0] | ITERM[3:0]  | ITERM[1]<br>1 = 4mA     |                                                                                  | 0    | R/W  | REG_RST<br>or Watchdog |

|        |             | ITERM[0]<br>1 = 2mA     |                                                                                  | 1    | R/W  | REG_RST or Watchdog    |

## REG04

Register address: 0x04; R/W

PORV = 10100011

#### Table 8. REG04 Register Details

| BITS   | BIT NAME       | DESCRIPTION                | COMMENT                                 | PORV | TYPE  | RESET BY     |

|--------|----------------|----------------------------|-----------------------------------------|------|-------|--------------|

|        |                | VBAT_REG[5]                | Battery Charge Regulation Voltage Value | 1    | R/W   | REG_RST      |

|        |                | 1 = 480mV                  | (CV Mode) (n: 6 bits):                  |      |       | or Watchdog  |

|        |                | VBAT_REG[4]                | = 3.6V + 0.015n (V)                     | 0    | R/W   | REG_RST      |

|        |                | 1 = 240mV                  |                                         |      |       | or Watchdog  |

|        |                | VBAT_REG[3]                | Offset: 3.60V                           | 1    | R/W   | REG_RST      |

| D[7:2] | VBAT REG[5:0]  | 1 = 120mV                  | Range: 3.60V (000000) - 4.545V (111111) | ,    | 17/77 | or Watchdog  |

| D[1.2] | VDAT_INEO[0.0] | VBAT_REG[2]                | Default: 4.2V (101000)                  | 0    | R/W   | REG_RST      |

|        |                | 1 = 60mV                   |                                         | U    | 17/77 | or Watchdog  |

|        |                | VBAT_REG[1]                |                                         | 0    | R/W   | REG_RST      |

|        |                | 1 = 30mV                   |                                         | U    | FK/VV | or Watchdog  |

|        |                | VBAT_REG[0]                |                                         | 0    | DAM   | REG_RST      |

|        |                | 1 = 15mV                   |                                         | 0    | R/W   | or Watchdog  |

|        |                | Pre-Charge to Fast Charge  |                                         |      |       |              |

| D[4]   | VDAT DDE       | Threshold                  |                                         | 4    | R/W   | REG_RST      |

| D[1]   | VBAT_PRE       | 0 = 2.8V                   |                                         | I    | FK/VV | or Watchdog  |